# **UNIT-II**

# SYNCHRONOUS SEQUENTIAL LOGIC

Introduction to sequential circuit-Flipflops -Operation and Excitation Tables.

Triggering of FF. Analysis and design of clocked sequential circuits-Design-Moor/Mealy models, state minimization, s t a t e assignment, circuit implementation-Registers-Counters

# 1. Introduction to sequential circuit:

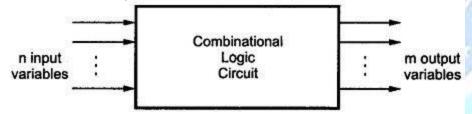

In *combinational logic circuits*, the outputs at any instant of time depend only on the input signals present at that time. For any change in input, the output occurs immediately.

Fig. 3.7 Block diagram of a combinational circuit

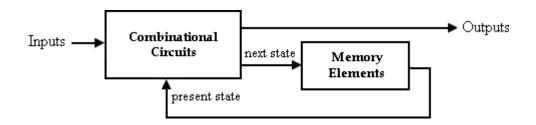

In *sequential logic circuits*, it consists of combinational circuits to which storage elements are connected to form a feedback path. The storage elements are devices capable of storing binary information either 1 or 0. The information stored in the memory elements at any given time defines the present state of the sequential circuit. The present state and the external circuitdetermine the output and the next state of sequential circuits.

#### ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

## Sequential Circuit- Block Diagram

Thus in sequential circuits, the output variables depend not only on the The rotary channel selected knob on an old-fashioned TV is like a combinational. Its output selects a channel based only on its current input – the position of the knob. The channel- up and channel-down push buttons on a TV is like a sequential circuit. The channel selection depends on the past sequence of up/downpushes.

The comparison between combinational and sequential circuits is given intable below.

| S.No | Combinational logic                                            | Sequential logic                                                      |

|------|----------------------------------------------------------------|-----------------------------------------------------------------------|

| 1    | The output variable, at all times                              | The output variable depends not only                                  |

|      | depends on the combination of                                  | on the present input but also depend                                  |

|      | input variables.                                               | upon the past history of inputs.                                      |

| 2    | Memory unit is not required.                                   | Memory unit is required to store the past history of input variables. |

| 3    | Faster in speed.                                               | Slower than combinational circuits.                                   |

| 4    | Easy to design.                                                | Comparatively harder to design.                                       |

| 5    | Eg. Adder, subtractor, Decoder, Encoders, Magnitude comparator | Eg. Shift registers, Counters                                         |

## ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

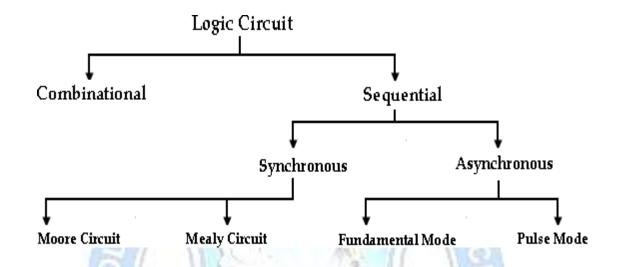

| S.No | Synchronous sequential circuits                                                        | Asynchronous sequential circuits                                                  |

|------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 1    | Memory elements are clocked Flip-Flops.                                                | Memory elements are either unclocked flip-flops (Latches) or time delay elements. |

| 2    | The change in input signals can affect memory element upon activation of clock signal. | The change in input signals can affect memory element at any instant of time.     |

| 3    | The maximum operating speed of clock depends on time delays involved.                  | Because of the absence of clock, it can operate faster than synchronous circuits. |

| 4    | Easier to design                                                                       | More difficult to design                                                          |

# DEVIVISALAKSHI.G-AP/CSE/RCET