## CLASSIFICATIONOFSYNCHRONOUSSEQUENTIALCIRCUIT:

In synchronous or clocked sequential circuits, clocked Flip-Flops are used as memory elements, which change their individual states in synchronism with the periodic clock signal. Therefore, the change in states of Flip-Flop and change in state of the entire circuits accurate the transition of the clock signal.

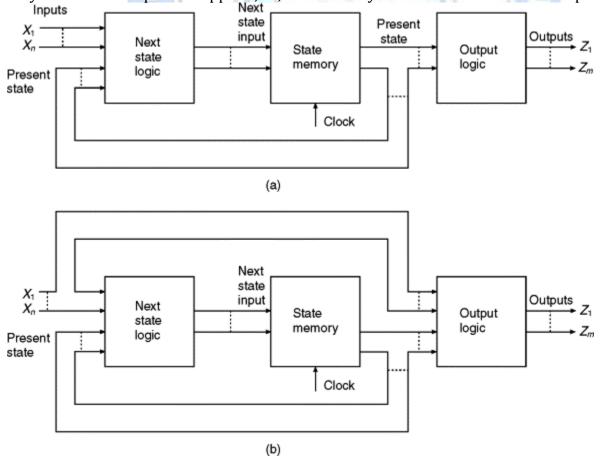

The synchronous or clocked sequential networks are represented by two models.

**Moore model:** The output depends only on the present state of the Flip-Flops. **Mealy model:** The output depends on both the present state of the Flip-Flops and on the inputs

#### Moore model:

In the Moore model, the outputs are a function of the present state of the Flip-Flops only. The out put depends only on present state of FlipFlops, it appears only after the clock pulse is applied, i.e., it varies in synchronism with the clock input.

## Mealymodel:

In the Mealy model , the outputs are functions of both the present state of the  $\mbox{\it Flip-}$  Flops and inputs

Difference between Moore and Mealymodel

| S.No | Moore model                         | Mealy model                               |  |  |  |

|------|-------------------------------------|-------------------------------------------|--|--|--|

| 1    | Its output is a function of present | Its output is a function of present state |  |  |  |

|      | State only.                         | As well as present input.                 |  |  |  |

| 2    | An input change does not affect the | Input changes may affect the output of    |  |  |  |

|      | output.                             | The circuit.                              |  |  |  |

| 3    | It requires more number of states   | It requires less number of states for     |  |  |  |

|      | For implementing same function.     | Implementing same function.               |  |  |  |

Mealy model

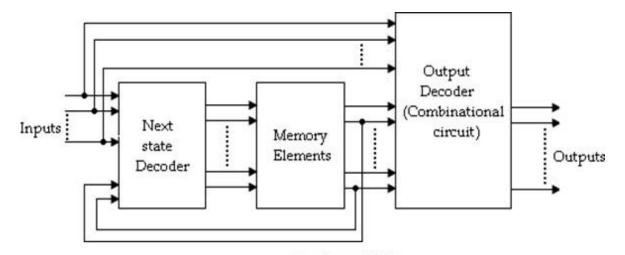

### ANALYSIS OF SYNCHRONOUS SEQUENTIAL CIRCUIT:

#### **ANALYSIS PROCEDURE:**

The synchronous sequential circuit analysis is summarizes as given below:

- 1. AssignastatevariabletoeachFlip-Flopinthesynchronoussequentialcircuit.

- 2. Write the excitation input functions for each Flip-Flop and also write the Moore/Mealy output equations.

- 3. Substitute the excitation input functions into the b is table equations for the Flip- Flops to obtain the next state output equations.

- 4. Obtain the state table and reduced form of the state table.

DEVIVISALAKSHI.G-AP/CSE/RCET

5. Draw the state diagram by using the second form of the state table.

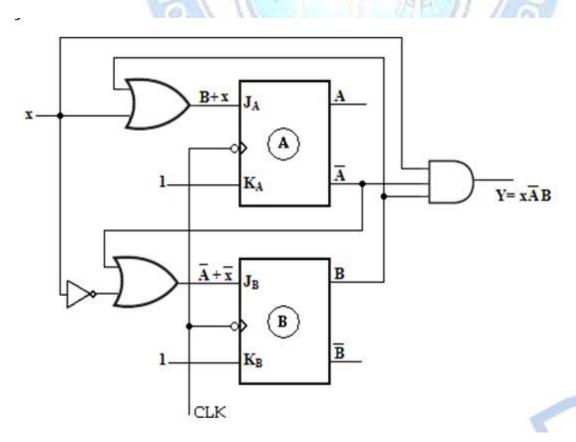

### **ANALYSISOFMEALYMODEL:**

A sequential circuit has two JK Flip-Flops A and B, one input(x) and one output(y).

1. A sequential circuit has two JK Flip-Flops A and B, one input(x) and one output the Flip-Flop input functions are,

JA=B+x JB=A'+x'

KA=1 KB=1

And the circuit output function, **Y=x A'B**.

- a) Draw the logic diagram of the Mealy circuit,

- b) Tabulate the state table,

- c) Draw the state diagram.

## **Logic Diagram:**

DEVIVISALAKSHI.G-AP/CSE/RCET

## State table:

| Pre: | sent<br>æ | Inp<br>ut | Flip-Flop Inputs |          |              | Flip-Flop Inputs Next state |            |            | Out<br>put |

|------|-----------|-----------|------------------|----------|--------------|-----------------------------|------------|------------|------------|

| A    | В         | X         | JA=B+<br>x       | KA=<br>1 | JB=A'<br>+x' | KB<br>=1                    | A(t<br>+1) | B(t<br>+1) | Y=xA<br>'B |

| 0    | 0         | 0         | 0                | 1        | 1            | 1                           | 0          | 1          | 0          |

| 0    | 0         | 1         | 1                | 1        | 1            | 1                           | 1          | 1          | 0          |

| 0    | 1         | 0         | 1                | 1        | 1            | 1                           | 1          | 0          | 0          |

| 0    | 1         | 1         | 1                | 1        | 1            | 1                           | 1          | 0          | 1          |

| 1    | 0         | 0         | 0                | 1        | 1            | 1                           | 0          | 1          | 0          |

| 1    | 0         | 1         | 1                | 1        | 0            | 1                           | 0          | 0          | 0          |

| 1    | 1         | 0         | 1                | 1        | 1            | 1                           | 0          | 0          | 0          |

| 1    | 1         | 1         | 1                | 1        | 0            | 1                           | 0          | 0          | 0          |

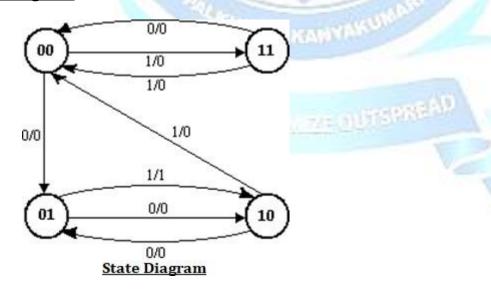

**Reduced State Table**

| L | 100   |          |    |         |        |      |     |     |

|---|-------|----------|----|---------|--------|------|-----|-----|

|   | Prese | nt state |    | N<br>st | Output |      |     |     |

|   |       |          | X= | x=0     |        |      | x=0 | x=1 |

|   | A     | В        | A  | В       | A      | В    | y   | y   |

|   | 0     | 0        | 0  | 1       | 77 1 W | 1    | 0   | 0   |

|   | 0     | 1        | 1  | 0       | 1      | 0    | 0   | 1   |

|   | 1     | 0        | 0  | 1       | 0      | 0    | 0   | 0   |

|   | 1     | 1        | 0  | 0       | 0      | 0 // | 0   | 0   |

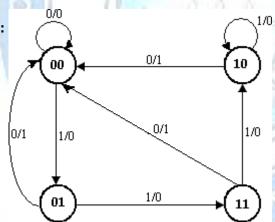

# **State Diagram:**

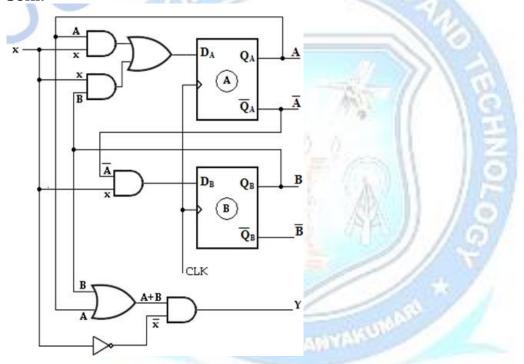

2. A sequential circuit with two 'D' Flip-Flops A and B, one input(x) and one

DEVIVISALAKSHI.G-AP/CSE/RCET

output(y). The Flip-Flop input functions are:

DA = Ax + B

xDB=A'x

and the circuit output function is, Y=(A+B)x'.

- (a) Draw the logic diagram m of the circuit,

- (b) Tabulate the state table,

- (c) Draw the state diagram.

## 3. Soln:

| Present state |   | Inpu<br>t | Flip-FlopInputs     |   | nextstate |        | Output    |

|---------------|---|-----------|---------------------|---|-----------|--------|-----------|

| A             | В | X         | DA=<br>Ax+Bx DB=A'x |   | A(t+1)    | B(t+1) | Y=(A+B)x' |

| 0             | 0 | 0         | 0                   | 0 | 0         | 0      | 0         |

| 0             | 0 | 1         | 0                   | 1 | 0         | 1      | 0         |

| 0             | 1 | 0         | 0                   | 0 | 0         | 0      | 1         |

| 0             | 1 | 1         | 1                   | 1 | 1         | 1      | 0         |

| 1             | 0 | 0         | 0                   | 0 | 0         | 0      | 1         |

| 1             | 0 | 1         | 1                   | 0 | 1         | 0      | 0         |

| 1             | 1 | 0         | 0                   | 0 | 0         | 0      | 1         |

| 1             | 1 | 1         | 1                   | 0 | 1         | 0      | 0         |

DEVIVISALAKSHI.G-AP/CSE/RCET

| Prese | nt state |    | Nex | Output |    |     |     |

|-------|----------|----|-----|--------|----|-----|-----|

|       |          | X= | =0  | X=     | =1 | x=0 | x=1 |

| A     | A B      |    | В   | A      | В  | Y   | Y   |

| 0     | 0        | 0  | 0   | 0      | 1  | 0   | 0   |

| 0     | 1        | 0  | 0   | 1      | 1  | 1   | 0   |

| 1     | 0        | 0  | 0   | 1      | 0  | 1   | 0   |

| 1     | 1        | 0  | 0   | 1      | 0  | 1   | 0   |

Second for m of state table

# **State Diagram:**

### Second for m of state table

State Diagram:

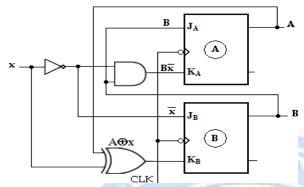

# 3. A sequential circuit has two JK Flip-Flop A and B. the

Flip-Flop input functions are: JA=B JB=x'

$$KA=Bx'$$

$KB=A?x$ .

- (a) Draw the logic diagram of the circuit,

- (b) Tabulate the state table,

- (c) Draw the state diagram.

### Soln:

DEVIVISALAKSHI.G-AP/CSE/RCET

# Logic diagram

The output function is not given in the problem. The output of the Flip-

Flops maybe considered as the output of the circuit.

#### **State table:**

| Pres ent state Inp u |   |   |      | Flip  | Next state |        |        |            |

|----------------------|---|---|------|-------|------------|--------|--------|------------|

| A                    | В | X | JA=B | KA=Bx | JB= x'     | KB=A x | A(t+1) | B(t+<br>1) |

| 0                    | 0 | 0 | 0    | 0     | 1          | 0      | 0      | 1          |

| 0                    | 0 | 1 | 0    | 0     | 0          | 1      | 0      | 0          |

| 0                    | 1 | 0 | 1    | 1     | 1          | 0      | 1 //   | 1          |

| 0                    | 1 | 1 | 1\\  | 0     | 0          | 1      | 1/1/   | 0          |

| 1                    | 0 | 0 | 0    | 0     | 1          | 1      | 1      | 1          |

| 1                    | 0 | 1 | 0    | 0     | 0          | 0      | 1      | 0          |

| 1                    | 1 | 0 | 1    | 1     | 1          | 1      | 0      | 0          |

| 1                    | 1 | 1 | 1    | 0     | 0          | 0      | 1      | 1          |

| Pres |   | Nex<br>t<br>stat<br>e |             |             |   |  |  |

|------|---|-----------------------|-------------|-------------|---|--|--|

|      |   | :                     | X<br>=<br>0 | X<br>=<br>1 |   |  |  |

| A B  |   | A                     | В           | A           | В |  |  |

| 0    | 0 | 0                     | 1           | 0           | 0 |  |  |

| 0 1  |   | 1                     | 1           | 1           | 0 |  |  |

| 1 0  |   | 1                     | 1           | 1           | 0 |  |  |

| 1    | 1 | 0                     | 0           | 1           | 1 |  |  |

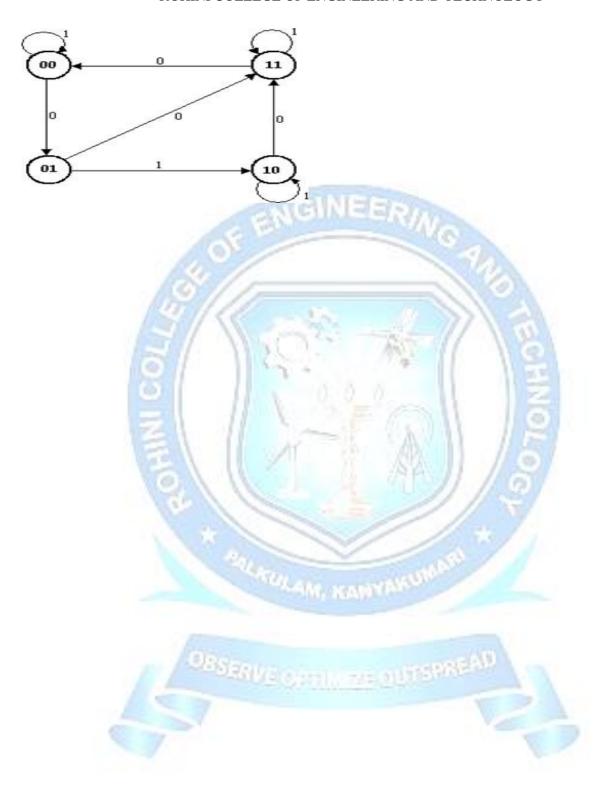

# **State Diagram**

DEVIVISALAKSHI.G-AP/CSE/RCET

DEVIVISALAKSHI.G-AP/CSE/RCET

CS3351-DIGITAL PRINCIPLES AND COMPUTER ORGANIZATION