## **Operation of Basic Phase Locked Loop**

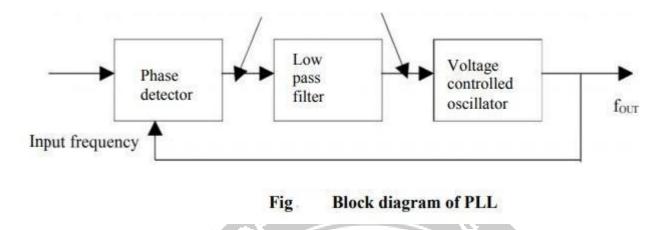

The PLL consists of i) Phase detector ii) LPF iii) VCO. The phase detector or comparator compares the input frequency  $f_{IN}$  with feedback frequency  $f_{OUT}$ . The output of the phase detector is proportional to the phase difference between  $f_{IN} \& f_{OUT}$ . The output of the phase detector is a dc voltage & therefore is often referred to as the error voltage. The output of the phase detector is then applied to the LPF, which removes the high frequency noise and produces a dc level. This dc level in turn, is input to the VCO. The output frequency of VCO is directly proportional to the dc level. The VCO frequency is compared with input frequency and adjusted until it is equal to the input frequencies.PLL goes through 3 states, i) free running ii) Capture iii) Phase lock.

Before the input is applied, the PLL is in free running state. Once the input frequency is applied the VCO frequency starts to change and PLL is said to be in the capture mode. The VCO frequency continuous to change until it equals the input frequency and the PLL is in phase lock mode. When Phase locked, the loop tracks any change in the input frequency through its repetitive action.

If an input signal vs of frequency fs is applied to the PLL, the phase detector compares the phase and frequency of the incoming signal to that of the output vo of the VCO. If the two signals differ in frequency of the incoming signal to that of the output vo of the VCO. The phase detector is basically a multiplier and produces the sum  $(f_s + f_o)$  and difference  $(f_s - f_o)$  components at its output. The high frequency component  $(f_s + f_o)$  is removed by the low pass filter and the difference frequency component is amplified then applied as control voltage v<sub>c</sub> to VCO.

The signal  $v_c$  shifts the VCO frequency in a direction to reduce the frequency difference between fs and  $f_o$ . Once this action starts, we say that the signal is in the capture range. The VCO continues to change frequency till its output frequency is exactly the same as the input signal frequency. The circuit is then said to be locked. Once locked, the output frequency  $f_o$  of VCO is identical to fs except for a finite phase difference  $\varphi$ . This phase difference  $\varphi$  generates a corrective control voltage vc to shift the VCO frequency from f0 to

fs and thereby maintain the lock. Once locked, PLL tracks the frequency changes of the input signal. Thus, a PLL goes through three stages (i) free running, (ii) capture and (iii) locked or tracking.

**Capture range:** The range of frequencies over which the PLL can acquire lock with an input signal is called the capture range. This parameter is also expressed as percentage of fo.

**Pull-in time:** The total time taken by the PLL to establish lock is called pull-in time. This depends on the initial phase and frequency difference between the two signals as well as on the overall loop gain and loop filter characteristics.

**Lock-in Range:** Once the PLL is locked, It can track frequency changes in the incoming signals. The range of frequencies over which the PLL can maintain lock with the incoming signal is called the lock in range or tracking range.

**Closed Loop Analysis of PLL:**

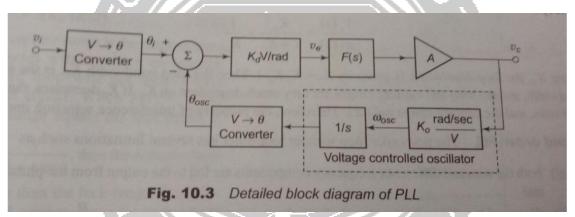

The i/p sinusoidal gain V<sub>i</sub> is given as

```

V_i = V_p \sin(\omega t + \theta)

```

If the phase shift of the signal at the VCO o/p is  $\theta_{osc}$ , then the average value of the o/p of phase detector is

$$V_e = K_d(\theta_i - \theta_{osc}) \text{ pre-ND}$$

where  $\theta_i \& \theta_{osc} \to phase shift$

The phase of the signal at the o/p of VCO as a function of time is equal to integral of the VCO o/p frequency & can be expressed as

$$\omega_{osc(t)} = \frac{d\theta_{osc(t)}}{dt}$$

$$d\theta_{osc(t)} = \omega_{osc(t)}dt$$

$$\int d\theta_{osc(t)} = \int \omega_{osc(t)}dt + \theta_{osc at t=0}$$

$$\theta_{osc(t)} = \int \omega_{osc(t)} dt + \theta_{osc at t=0}$$

The integral component is represented as 1/S inside the VCO block. Oscillator frequency  $\omega_{osc}$  & the dc control voltage V<sub>c</sub> are related by

$$\omega_{osc} = \omega_c + K_o V_c$$

where,  $\omega_c \rightarrow$  centre or free running angular frequency,

that results when  $V_c = 0 \& K_o$  is the VCO gain in rad/sec per volt.

Then the closed loop transfer function of PLL

$$\frac{V_c(s)}{\theta_i(s)} = \frac{K_d F(S) A}{1 + K_d A F(S) \frac{K_o}{S}} = \frac{SK_d F(S) A}{S + K_d A F(S) K_o}$$

Response of the loop to frequency variation at i/p than phase.

$$\frac{V_c(s)}{\omega_i(s)} = \frac{V_c(S)}{S\theta_i(S)} = \frac{K_d F(S) A}{S + K_d A F(S) K_o}$$

$$\omega_i = \frac{d\theta_i}{dt} \stackrel{\&}{=} \omega_i(s) = s\theta_i(s)$$

F(S)=0,with the loop having a first order low pass frequency response.

$$\frac{V_{c}(s)}{\omega_{i}(s)} = \frac{K_{v}}{S + K_{v}} X \frac{1}{K_{o}}$$

$$K_{v} \rightarrow loop \ bandwidth.$$

$$K_{v} = K_{o}K_{d}A$$

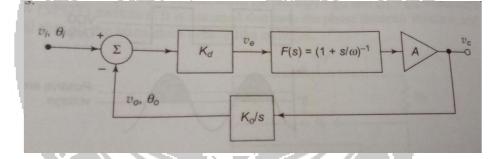

## Second Order PLL:

The first order loop without loop-filter has several limitations.

- 1. Both the sum & difference frequency components are fed to the o/p from the phase detector.

- 2. All out-of band interfering signals from the i/p will appear shifted in frequency at the o/p.

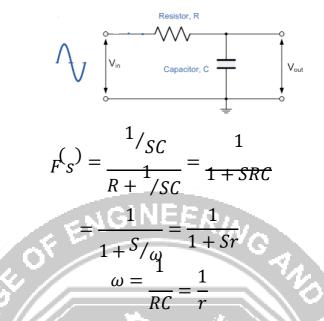

The most common configuration of monolithic PLL in the second order loop with a loop –filter F(s) of a simple single-pole LPF realized with a resistor R & a Capacitor C in Fig

The resulting block diagram of the second order PLL using single-pole loop filter.

## Loop Lock-Range & Capture Range:

The loop lock-range is represented as the range of frequency about  $\omega_o$  for which PLL maintains the relationship

$$\omega_i = \omega_{osc}$$

If the phase detector can determine the phase difference between  $\theta_i \& \theta_{osc}$ Over a  $\pm \pi$  range ,then the lock-range is defined as

$$\omega_L = \pm \Delta m_{osc}$$

$$= K_d A K_o(\pm \frac{\pi}{2})$$

$$= \pm K_v(\frac{\pi}{2})$$

The capture range is the range of i/p frequencies with in which a initially unlocked loop will get locked with an i/p signal. When F(s)=1, the capture range equals the lock-range. If  $F(S) = \frac{1}{1+S/m_i}$ , then the capture range is smaller than the lock-range.