### 5.3 INTERRUPT PROGRAMMING IN 8051

The Microcontroller can serve several devices. The Interrupt is the method to indicate the microcontroller by sending an interrupt signal. After receiving an interrupt, the microcontroller interrupts whatever it is doing and serves the device. The program associated with the interrupt is called the interrupt service routine (ISR). When an interrupt is invoked, the microcontroller runs the interrupt service routine. For every interrupt, there is a fixed location set aside to hold the addresses of ISRs.

The following events will cause an interrupt:

- 1. Timer 0 Overflow.

- 2. Timer 1 Overflow.

- 3. Reception/Transmission of Serial Character.

- 4. External Event 0.

- 5. External Event 1.

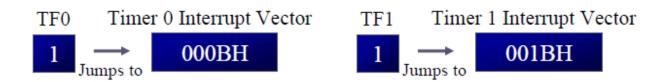

To distinguish between various interrupts and executing different code depending on what interrupt was triggered, 8051may be jumping to a fixed address when a given interrupt occurs as shown in Table 5.3.1.

| Interrupt                            | ROM Location (Hex) | Pin                   | Flag Clearing         |

|--------------------------------------|--------------------|-----------------------|-----------------------|

| Reset                                | 0000               | 9                     | Auto                  |

| External hardware interrupt 0 (INT0) | 0003               | P3.2 (12)             | Auto                  |

| Timer 0 interrupt (TF0)              | 000B               | TO THE REAL PROPERTY. | Auto                  |

| External hardware interrupt 1 (INT1) | 0013               | P3.3 (13)             | Auto                  |

| Timer 1 interrupt (TF1)              | 001B               |                       | Auto                  |

| Serial COM interrupt (RI and TI)     | 0023               | regionics.            | Programmer clears it. |

Table 5.3.1 Interrupt Vector Table for 8051

[Source: "The 8051Microcontroller and Embedded Systems: Using Assembly and C" by Mohamed Ali Mazidi, Janice Gillispie Mazidi, Rolin McKinlay, pg.no.320]

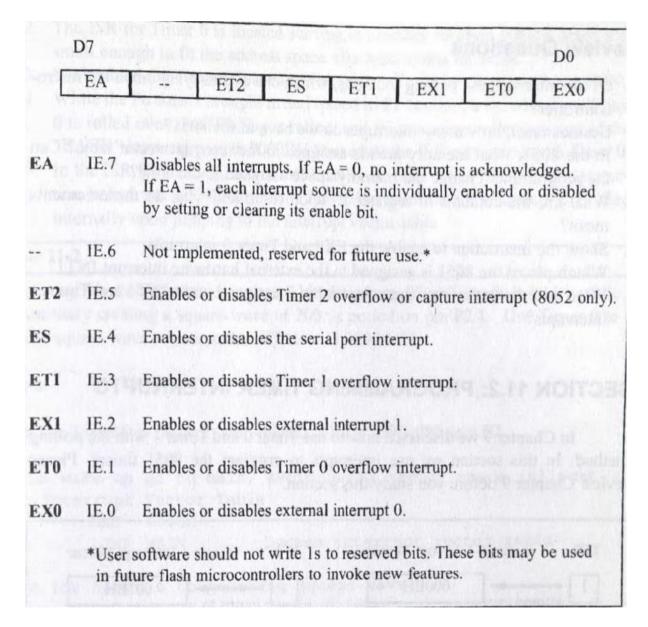

### ENABLING AND DISABLING AN INTERRUPT

Upon reset all interrupts are disable, meaning that known will be responded to by the microcontroller if they are activated. The Interrupt must be enabled by software in order for microcontroller to respond to them there is a register called IE that is responsible for enabling and disabling the interrupts as shown in Figure 5.3.1

Figure 5.3.1 Interrupt Enable(IE) Register

[Source: "The 8051Microcontroller and Embedded Systems: Using Assembly and C" by Mohamed Ali Mazidi, Janice Gillispie Mazidi, Rolin McKinlay, pg.no.321]

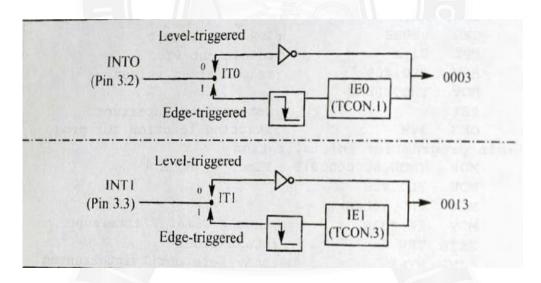

# PROGRAMMING EXTERNAL HARDWARE INTERRUPTS

The 8051 has two external hardware interrupts PIN 12 (P3.2) and Pin 13 (P3.3), designated as INT0 and INT1. Upon activation of these pins, the 8051 finishes the

execution of current instruction whatever it is executing and jumps to the vector table to perform the interrupt service routine.

### TYPES OF INTERRUPT

- 1)Level-TriggeredInterrupt

- 2)Edge -Triggered Interrupt

# LEVEL-TRIGGERED INTERRUPT

In this mode, INTO and INT1 are normally high and if the low level signal is applied to them, it triggers the Interrupt. Then the microcontroller stops and jumps to the interrupt vector table to service that interrupt. The low-level signal at the INT pin must be removed before the execution of the last instruction of the ISR, RETI. Otherwise, another interrupt will be generated. This is called a level-triggered or level-activated interruptandis the default mode upon reset

Figure 5.3.2 Activation of INT0 and INT1

[Source: "The 8051Microcontroller and Embedded Systems: Using Assembly and C" by Mohamed Ali Mazidi, Janice Gillispie Mazidi, Rolin McKinlay, pg.no.326]

# **EDGE -TRIGGERED INTERRUPT**

Upon reset 8051 makes INT0 and INT1 low l Level-Triggered Interrupt. To make them Edge -Triggered Interrupt, we must program the bits of the TCON Register. The TCON register holds among other bits and IT0 and IT1 flags bit the determine level- or edge triggered mode. IT0 and IT1 are bits D0 (TCON.0) and D2(TCON.2) of the TCON Register respectively.

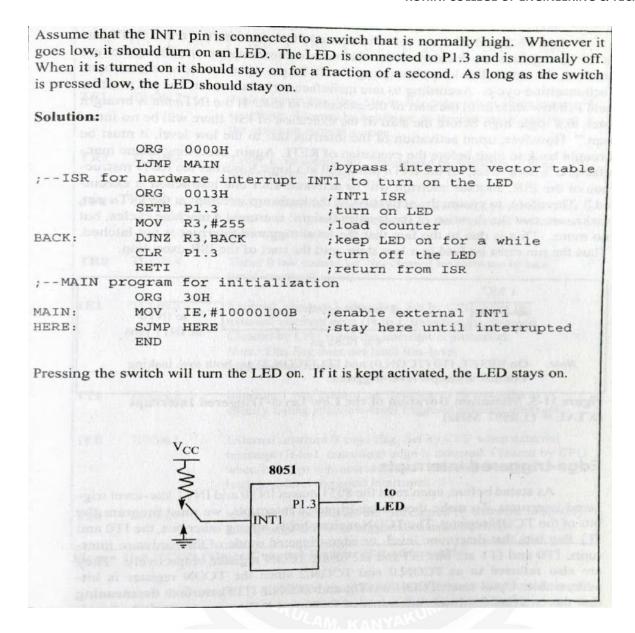

Figure 5.3.3 Example for Level triggered Interrupt

[Source: "The 8051Microcontroller and Embedded Systems: Using Assembly and C" by Mohamed Ali Mazidi, Janice Gillispie Mazidi, Rolin McKinlay, pg.no.327]

#### SERIAL COMMUNICATION INTERRUPT

**TI** (**transfer interrupt**) is raised when the stop bit is transferred indicating that the SBUF register is ready to transfer the next byte

**RI** (**received interrupt**) is raised when the stop bit is received indicating that the received byte needs to be picked up before it is lost (overrun) by new incoming serial data

In the 8051 there is only one interrupt set aside for serial communication ,used for both sending and receiving data.

If the interrupt bit in the IE register (IE.4) is enabled, when RI or TI is raised the 8051 gets interrupted and jumps to memory location 0023H to execute the ISR

In that ISR we must examine the TI and RI flags to see which one caused the interrupt and respond accordingly.

```

example 11-c

Write a program in which the 8051 reads data from P1 and writes it to P2 continuously

while giving a copy of it to the serial COM port to be transferred serially. Assume that XTAL = 11.0592 MHz. Set the band rate at 9600.

Solution:

ORG

LJMP

MAIN

23H

; jump to serial interrupt ISR

LJMP SERIAL

SERIAL

30H

P1,#0FFH

TMOD,#20H

TH1,#0FDH

SCON,#50H

ORG

MOV

MOV

;make P1 an input

;timer 1, mode 2(a

MAIN:

TMOD, #20H ;timer 1, mode 2(auto-re

TH1, #0FDH ;9600 baud rate

SCON, #50H ;8-bit, 1 stop, REN enab

IE, #10010000B ;enable serial interrupt

part input port

1, mode 2(auto-reload)

baud rate

t, 1 stop, REN enabled

MOV

SETB TR1

timer

MOV

MOV

MOV

BACK:

A, P1

SBUF, A

;read data from port 1

;give a copy to SBUF

;send it to P2

;stay in loop indefinitely

MOV P2,A

SJMP BACK

ORG 100H

JB TI,TRANS

MOV A,SBUF

CLR RI

Serial Port ISR

SERIAL .

;jump if TI is high

;otherwise due to receive

;clear RI since CPU does not

;return from ISR

RETI

TRANS:

;clear TI since

;return from ISR

CPU does not

RETI

END

In the above program notice the role of TI and RI. The moment a byte is written into

In the above program notice the role of 11 and RI. The moment a byte is written into SBUF it is framed and transferred serially. As a result, when the last bit (stop bit) is transferred the TI is raised, which causes the serial interrupt to be invoked since the corresponding bit in the IE register is high. In the serial ISR, we check for both TI and RI since both could have invoked the interrupt. In other words, there is only one interrupt for both transmit and receive

```

Figure 5.3.4 Example for Serial Communication Interrupt

[Source: "The 8051Microcontroller and Embedded Systems: Using Assembly and C" by Mohamed Ali Mazidi, Janice Gillispie Mazidi, Rolin McKinlay, pg.no.334]

# TIMER INTERRUPTS

The timer flag (TF) is raised when the timer rolls over. In polling TF, we have to wait until the TF is raised. The microcontroller is tied down while waiting for TF to be raised, and cannot do anything else. If the timer interrupt in the IE register is enabled, whenever the timer rolls over, TF is raised. This avoids tying down the controller.

The microcontroller is interrupted in whatever it is doing, and jumps to the interrupt vector table to service the ISR.In this way, the microcontroller can do other task until it is notified that the timer has rolled over

```

Write a program that continuously gets 8-bit data from P0 and sends it to P1 while

simultaneously creating a square wave of 200 µs period on pin P2.1. Use Timer 0 to

create the square wave. Assume that XTAL = 11.0592 MHz.

Solution:

We will use Timer 0 in mode 2 (auto-reload). TH0 = 100/1.085 \mu s = 92.

;--Upon wake-up go to main, avoid using memory space ;allocat-

ed to Interrupt Vector Table

ORG 0000H

LJMP MAIN

; bypass interrupt vector table

;--ISR for Timer 0 to generate square wave

ORG 000BH ;Timer 0 interrupt vector table CPL P2.1 ;toggle P2.1 pin

RETI

;return from ISR

; -- The main program for initialization

MOV TMOD,#02H ;Timer 0, mode 2(auto-reload)

MOV P0,#0FFH ;make P0 an input port

MOV TH0,#-92 ;TH0=A4H for -92

MOV IE,#82H ;IE=10000010(bin) enable Timer 0

SETB TR0 ;Start Timer 0

MOV A,P0 ;get data from P0

MOV P1,A ;issue it to P1

MOV P1,A ;issue it to P1

SJMP BACK ;keep doing it

;loop unless interrupted by TFO

```

Figure 5.3.5 Example for Timer Interrupt

[Source: "The 8051Microcontroller and Embedded Systems: Using Assembly and C" by Mohamed Ali Mazidi, Janice Gillispie Mazidi, Rolin McKinlay, pg.no.323]